### Support Nuclei SoC in QEMU RISC-V Emulation

Gao Zhiyuan, Seoul National University Wang Jungqiang, PLCT lab, ISRC-CAS

芯来科技 NUCLEI

# **Nuclei Products and Offerings**

智能软件研究中心

Intelligent Software Research Center

中国科学院软件研究所 Institute of Software Chinese Academy of Sciences

O 芯来科技 O NUCLEI

- We chose Nuclei HummingBird (N307),

- GPIO, UART0, UART1

- QSPI0, QSPI1, QSPI2

- PWM0, PWM1, PWM2

- I2C, No MMU

- An alternative for ARM Cortex-M3/M4/M4F/M33.

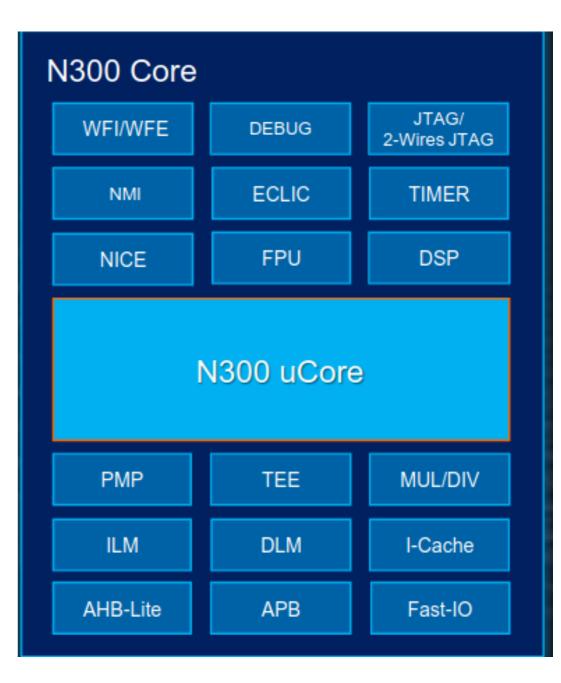

# What are needed to support Nuclei

- RISC-V CPU implementations: target/riscv/cpu.c overwriting configs for spec

- Extended customized CSR registers

- ECLIC: Enhanced Core Local Interrupt Controller

- Timer

- UART

- GPIO

- NMI: non-maskable interrupt

- ....

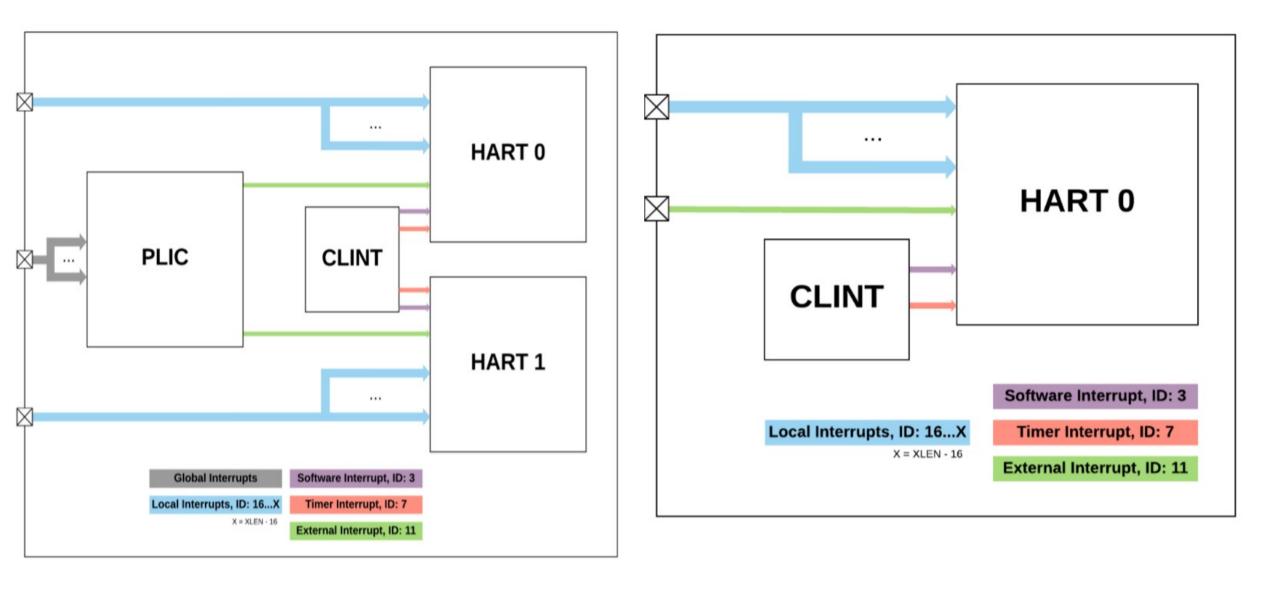

## **Interrupt Controllers**

- CLIC: Core Local Interrupt Controller (SiFive)

- CLINT: Core Local Interrupter (SiFive)

- PLIC: Platform Level Interrupt Controller (SiFive)

- ECLIC: Enhanced Core Local Interrupt Controller (Nuclei)

### Cores

- CLIC only adopted by SiFive E2

- series and S2 series

- Other SiFive cores support

- **CLINT and PLIC interrupt controller**

- ECLIC: only in Nuclei Cores

### **E** Cores

32-bit embedded cores MCU, edge computing, AI, IoT

Efficient performance: 5-6-stage, single-issue pipeline

3/5 Series

2 Series

gates

Power & area optimized:

2-3-stage, single-issue pipeline, as small as 13.5k

A 芯来科技 NUCLEI

智能软件研究中心

Intelligent Software Research Cente

|   | E3 Series                                      |   | S |

|---|------------------------------------------------|---|---|

| > | E34                                            | > | S |

|   | E31 features + single-precision floating point |   | S |

| > | E31                                            | > | S |

|   | Balanced performance and efficiency            |   | Ŀ |

#### **S** Cores

64-bit embedded cores Storage, AR/VR, machine learning

#### S5 Series

S54

S51 features + double-precision floating point

S51

\_ow-power 64-bit MCU core

#### S2 Series

> S21

Area optimized 64-bit processor

> E21

E24

>

E2 Series

E20 features + User Mode, Atomics, Multiply, TIM

E21 features + single-precision floating point

> E20

Our smallest, most efficient core

A 芯来科技 NUCLEI

## CLIC vs. CLINT vs. ECLIC

- CLINT:

- Fixed priority scheme based on source id

- Only software and timer interrupts. Other interrupts are wired directly to the CPU.

- CLIC:

- Programmable interrupt levels, priorities

- Support nested interrupts (preemption)

- ECLIC:

- 4096 interrupt sources

- Configurable priority, enable/disable, level-triggered or edge-triggered

- Nested Interrupts and tail-chaining

### **ECLIC Implementation**

- ECLIC class init

- Nuclei device create a ECLIC device

- register properties (e.g. num\_sources, size)

- connect to sysbus

- ECLIC device realize

- Allocate space for registers per input source (e.g. clicintattr, clicintie, clicintip)

- connect eclic with GPIO/UART/Timer for related interrupts

- When an interrupt happens,

- IRQ is added to pending array of irqs

- Update the array of IRQs, deal with nested or tail chaining cases

## **Registers in ECLIC**

- Registers per interrupt source

- clicintip: the interrupt polarity, deciding whether IRQs are triggered together with clicintattr

- clicintie: enables or disables the interrupt source

- clicintattr: defines a level-triggered, rising-edge triggered, or falling-edge triggered IRQ

- clicintctl: contains priority and level values

- Registers in ECLIC

- cliccfg: configures effective bits within clicintctl for interrupt priority calculation

- clicinfo: read-only register defining hardware version, # of sources, effective bits in clicintctl

- mth: defining the level threshold, where lower-leveled interrupts are disabled

```

static void nuclei eclic update intip(NucLeiECLICState *eclic, int irg, int new intip)

{

eclic->clicintip[irq] = !!new intip;

nuclei_eclic_next_interrupt(eclic);

}

static void nuclei eclic next interrupt(NucLeiECLICState *eclic)

RISCVCPU *cpu = RISCV CPU(gemu get cpu(0));

ECLICActiveInterrupt *active = eclic->active list;

size_t active count = eclic->active count;

int level = 0, priority = 0;

while (active count) {

clicintctl decode(eclic, active->clicintctl, &level, &priority);

if (eclic->clicintip[active->irq]) {

riscv cpu eclic interrupt(cpu, active->irg | level<<12);

return;

/* check next enabled interrupt */

active count--;

active++;

}

/* clear pending interrupt for this hart */

riscv cpu eclic interrupt(cpu, -1);

```

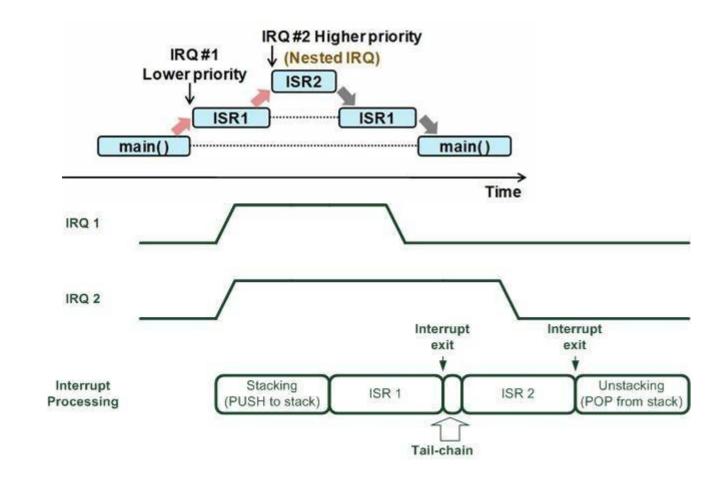

## **Nested Interrupt and Tail-chaining**

- Nested Interrupt: newly arrived interrupt (IRQ#2) has a higher priority.

ISR restores execution after IRQ #1 finishes.

- Tail-chaining: IRQ #2 has a lower priority. IRQ #1 passes the context to IRQ #2, so the context saving/restoring procedure can be saved between IRQ #1 and IRQ #2